# Journal of Engineering and Sustainable Development

Vol. 23, No.06, November 2019 ISSN 2520-0917 https://doi.org/10.31272/jeasd.23.6.1

# ANALYSIS and SIMULATION of MOSFET DIFFERENTIAL AMPLIFIER

## Dr. Muneer Aboud Hashem

Assistant Prof., Electrical Engineering Department, Mustansiriyah University, Baghdad, Iraq.

Received 24/1/2018

Accepted in revised form 9/10/2018

Published 1/11/2019

Abstract: With the evolution of electronics today, a MOSFET transistor is useful in many applications such as computers due to several advantages. In this research, an NMOS transistor differential amplifier circuit with passive load that uses a modified Wilson current mirror as a biasing circuit is analyzed, designed and implemented. The width-to-length ratios of transistors are calculated by considering the voltage and current values at the output of the biasing circuit, and parameters such as conduction parameter, base width modulation parameter, and threshold voltage. A MATLAB version 8.1.0.604(R2010a) programming tool is employed for calculations and the simulations are carried out via Multisim 9 software tool. The output resistance obtained for current mirror is 2.297 M $\Omega$ . CMRR, output resistance, and power dissipation for differential amplifier circuit are 33.351 dB, 61.274 k $\Omega$  and 6.66 mW, respectively. The results show that the width-to-length ratio, differential gain and common mode rejection ratio are decreased with decreasing applied voltage at the output of the biasing circuit while approximately same values obtained for output resistance and common mode gain. The results show a good agreement between the measured values from simulation and the calculated one from design.

Key Words: NMOS Transistor, Current Mirror, Differential Pair, Common Mode Rejection Ratio

# تحليل ومحاكاة المضخم التفاضلي الذي يستخدم الترانزستور المجالي نوع معدن- اوكسيد- شبه موصل

الخلاصة: مع تطور الالكترونيات في يومنا هذا، يعتبر الترانسستور المجالي نوع معدن- أوكسيد- شبه موصل مفيد في كثير من التطبيقات مثل الحواسيب لمزاياه المتعددة. في هذا البحث، تم تحليل وتصميم وتنفيذ دائرة المضخم التفاضلي مع الحمل الخامل، ذات الترانسستور مثل الحواسيب لمزاياه المتعددة. في هذا البحث، تم تحليل وتصميم وتنفيذ دائرة المضخم التفاضلي مع الحمل الخامل، ذات الترانسستور معدن- أوكسيد- شبه موصل النوع السالب، والتي تستعمل دائرة مراة التيار Wilson المعدلة كدائرة انحياز. تم حساب نسبة العرض-الى- معدن- أوكسيد- شبه موصل النوع السالب، والتي تستعمل دائرة مراة التيار Wilson المعدلة كدائرة انحياز. تم حساب نسبة العرض-الى- معدن- أوكسيد- شبه موصل النوع السالب، والتي تستعمل دائرة مراة التيار ات عند خرج دائرة الانحياز اولا والمتغيرات مثل متغير التوصيل ومتغير تعديل عرض القاعدة وفولتية العتبة. استخدمت الاداة البرمجية (Wilson 8.10.604(R2010a) لغرض العرض الحسابات والتيات والتيات والتيار ات عند خرج دائرة الانحياز اولا والمتغيرات مثل متغير التوصيل ومتغير تعديل عرض القاعدة وفولتية العتبة. استخدمت الاداة البرمجية (MATLAB version 8.1.0.604(R2010a) لغرض العربات والتيات والتي والا عن خرض الغامل، في يومنا من وي معدن عرض القاعدة ونولتية العتبة. استخدمت الاداة البرمجية (Multisin 9.2000) عمد الخرج دائرة مراة التيار MM لغرض الحسابات واما المحاكاة فتمت عبر الاداة البرمجية (Multisin 9.2000) ومامة الخرج دائرة مراة التيار MM وي 2010 ما في دائرة المضخم التفاضلي فكان قلمة المستحصلة لمقومة الخرج دائرة مراة التيار MM في دائرة المضخم التفاضلي وكان قيمة نسبة رفض الوضع المشترك الك 3.33 العسبة ولقوم الغرب 4.300 ما في دائرة مراة الخرج 6.3200 ما في دائرة مالمن منه في دائرة المضخم التفاضلي وكان قلم دائرة من الوضع المشترك طالم القيمة المالحري في عمد مدن الوضع المشترك والما في ما في دائرة ما ما في دائرة المضخم التفاضلي في ماة دائرة ما وضع المشترك ما فقيمة المام ومدن الى القوم المول لتر انستور الحري ماة وكان كل ما في دائرة المضخم التفاضلي ونسبة رفض القيرت التائية فصان نسبة العرض-الى-الحرام ولكر ما ولفي ولماني وكان ما لقيمان كل ما لغرب الفول لي المول لتر الستور المن ما وي يابلي مانيم مان كل ما في دائرة النامي ونسبة رفض الوس الوسع المشترك مع نقصان الفولتية المطبقة

<sup>\*</sup>Corresponding Author muneraboud@yahoo.com

#### 1. Introduction

In integrated circuits, p- and n-types MOS (metal-oxide-semiconductor) current mirrors can be used as biasing and active load circuits. This circuit consists of a diode-

connected and perfectly matched transistors operated in saturation, and also at same temperature. A reference current is injected in the input and the output current is taken from the output of the mirror [1-3].

Different values of these currents can be obtained by designing width-to-length ratio, (W/L), of the MOS transistors. A high output resistance is an important parameter for these circuits; a value of 4.5 M $\Omega$  [4] is obtained for modified Wilson current mirror. The differential amplifier is an extremely common circuit in integrated circuits. The MOS version of this circuit consists of two transistors biased by current source, the sources of these transistors are connected together and the drains are connected to two resistors as passive load. The resistors operate the transistors in saturation and the whole circuit is biased from a current provided by current mirror circuit. The power dissipation of this circuit is 6.04 mW [5]. Active load may replaces resistors by transistors and the differential amplifier then has both p- and n-types transistors, i.e. CMOS amplifier (C; stands for complementary) [6-7]. As known, the differential amplifier has two inputs and two outputs; signals can be applied at its inputs. The output signals are out-of-phase and the amplified voltage values at outputs are according to difference between the inputs. The circuit operates from two supplies or even one supply. For high performance, suitable differential amplifiers can be analyzed, designed, and simulated for numerous applications [8-9].

## 2. Biasing Circuit Design

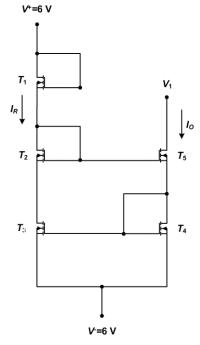

An improved NMOS Wilson current mirror is used as shown in "Fig. 1", transistor  $T_1$  is to provide reference current and the circuit is biased at  $\pm 6$  V.

Figure 1. Biasing circuit.

The specified parameters for designing NMOS transistors are;

- Conduction parameter  $k'_n = 80 \ \mu \text{A/V}^2$

- Base width modulation parameter  $\lambda_n = 0.02 \text{ V}^{-1}$

- Threshold voltage  $V_T = 1$  V.

The biasing currents are;

- Reference current  $I_R = 800 \,\mu\text{A}$

- Output current  $I_0 = 812 \,\mu\text{A}$

To calculate (W/L) for the transistors, consider first the voltage at the drain of  $T_5$  to be  $V_1 = 2$  V. Let the drain to source voltage of  $T_4$  is  $V_{DS5} = 4$  V, so

$$V_1 - V_{DS5} - V_{DS4} + 6 = 0$$

(1)

$$V_{DS4} = 4 V$$

Transistor  $T_4$  is a diode-connected transistor so gate-to-source voltages are  $V_{GS4} = 4$  V and  $V_{GS3} = 4$  V for matched  $T_3$  and  $T_4$  transistors. The ratio of output and established reference current is given by [10]

$$\frac{I_O}{I_R} = \frac{1 + \lambda_n V_{DS4}}{1 + \lambda_n V_{DS3}} \tag{2}$$

Using above values

$$\frac{812}{800} = \frac{1 + 0.02(4)}{1 + 0.02(V_{DS3})}$$

$$V_{DS3} = 3.202 \text{ V}.$$

Assuming that  $T_1$  and  $T_2$  are identical, so  $V_{GS1} = V_{GS2} = V_{GS}$ . From Kirchhoff's voltage law

$$V^{+} - V_{GS1} - V_{GS2} - V_{DS3} + V^{-} = 0$$

$$6 - 2V_{GS} - 3.2 + 6 = 0$$

$$V_{GS1} = V_{GS2} = 4.399 \text{ V}$$

(3)

$V_{GS5}$  is found from

$$V_{DS3} + V_{GS2} - V_{GS5} - V_{GS4} = 0$$

(4)

$V_{GS5} = 3.601 \text{ V}$

The obtained voltages set all transistors in the saturation region, (W/L) for transistors can be calculated as;

i- For  $T_1$  and  $T_2$ :  $V_{GS1} = V_{GS2} = 4.399$  V and  $V_{DS1} = V_{DS2} = 4.399$  V so (W/L) for these transistors are obtained from

$$I_{\rm R} = \frac{k'_n}{2} \left(\frac{W}{L}\right) (V_{GS} - V_T)^2 (1 + \lambda_n V_{DS})$$

$$\left(\frac{W}{L}\right)_1 = \left(\frac{W}{L}\right)_2 = 1.5911$$

(5)

ii- For  $T_3$ :  $V_{GS3} = 4$  V and  $V_{DS3} = 3.202$  V, from (5)

$$\left(\frac{W}{L}\right)_3 = 2.0885$$

iii- For  $T_4$  and  $T_5$ , (W/L) is determined from

$$I_{\rm O} = \frac{k'_n}{2} \left(\frac{W}{L}\right) (V_{GS} - V_T)^2 (1 + \lambda_n V_{DS})$$

(6)

Since  $V_{GS4} = 4 \text{ V}$ ,  $V_{DS4} = 4 \text{ V}$ ,  $V_{GS5} = 3.601 \text{ V}$ , and  $V_{DS5} = 4 \text{ V}$ , so

$$\left(\frac{W}{L}\right)_4 = 2.0885$$

and

$$\left(\frac{W}{L}\right)_5 = 2.7783$$

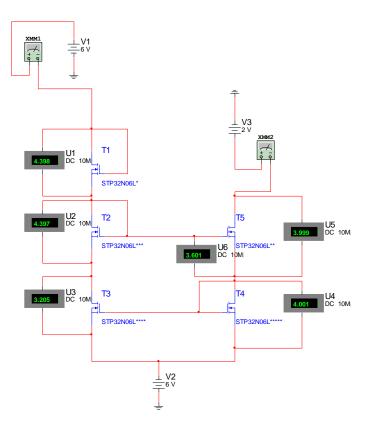

The calculated values above are obtained from MATLAB programming tool version 8.1.0.604(R2010a) [11] according to the specified parameters for design. The biasing circuit with Multisim 9 [12] is simulated in "Fig. 2".

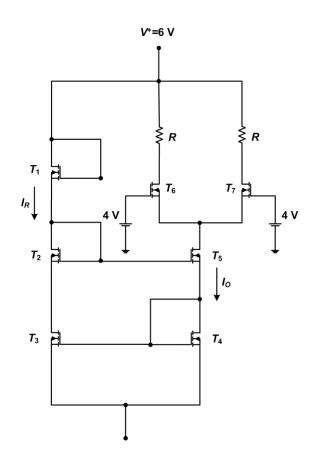

#### 3. Differential Circuit Design

The differential amplifier circuit consists of  $\pm 4$  V supply at the gates of identical transistors  $T_6$  and  $T_7$ , and two load resistors of  $5.1 \text{ k}\Omega$  each shown in Fig. 3. The differential pair is biased by constant current source  $I_0$  that is divided equally between  $T_6$  and  $T_7$ . The quiescent current in each of load resistors is the given by

$$I_{DQ} = \frac{I_0}{2} = 406 \,\mu\text{A}$$

then voltages at load resistors is  $V_R = 2.07$  V. The drain-to-source voltage at  $T_6$  is given by

$$V_{DS6} = V^+ - V_R - V_1 \tag{7}$$

hence  $V_{DS6} = 1.93$  V and  $V_{GS6} = 2$  V. From symmetry, the (W/L) ratio for  $T_6$  and  $T_7$ , which they are biased in the saturation region, is found from (6) as

$$406 = \frac{80}{2} \left(\frac{W}{L}\right) (2-1)^2 (1+(0.02)1.93)$$

$$\left(\frac{W}{L}\right)_6 = \left(\frac{W}{L}\right)_7 = 9.7729$$

Figure 2. Biasing circuit simulation.

# 4. Differential Gain, Common Mode Gain, and Common mode Rejection Ratio

The differential-mode gain is [10]

$$A_d = \frac{g_m R}{2} \tag{8}$$

where  $g_m$  is the transconductance given by

$$g_m = 2 \sqrt{\frac{k'_n}{2} \left(\frac{W}{L}\right) I_{DQ}} \tag{9}$$

Therefore  $g_m = 1.1 \text{ mA/V}$ , and  $A_d = 2.87$ . The common-mode gain is

$$A_C = \frac{-g_m R}{1 + 2g_m R_0} \tag{10}$$

where  $R_0$  is the output resistance given by

$$R_0 = \frac{1}{\lambda_n I_0} \tag{11}$$

so  $R_0 = 61.756 \text{ k}\Omega$ , and  $A_c = -0.0411$ . and the common-mode rejection ratio, CMRR, is

CMRR=20 log

$$\frac{A_d}{|A_c|} = 20 \log \frac{2.87}{0.041} = 36.88 \text{ dB}$$

Figure 3. Differential amplifier circuit.

### 5. Results

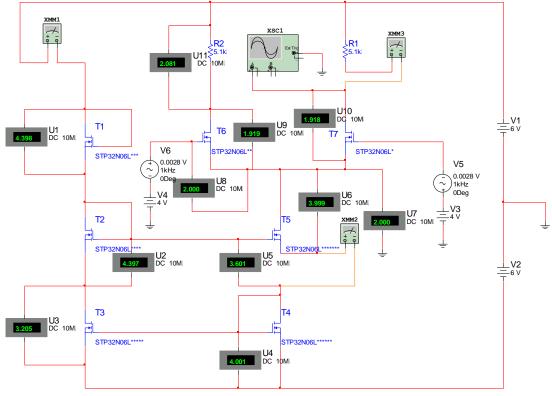

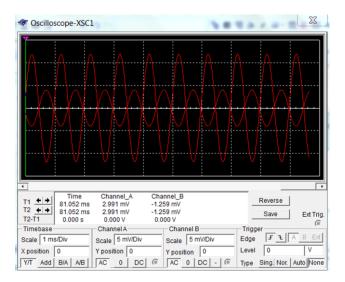

The complete designed circuit values are also accomplished with MATLAB computer program and it is simulated as shown in "Fig. 4". In this circuit, STP32N0GL power NMOS transistor type is used, an input dc common-mode voltage of 4 V is applied to  $T_6$  and  $T_7$  for specifying  $V_{GS6}$  and  $V_{GS7}$ . The measured reference current is 804 µA and the current source transistor  $T_5$  supplies a current of 816 µA. For the current mirror, the output resistance is 2.297 MΩ compared with 4.5 MΩ in [4]. For the differential-mode gain measurement, an input signal voltage of  $\pm 4$  mV is applied, this given in r.m.s values as 0.0028 V. The measured output signal voltage is about 16 mV,

so  $A_d = 16/8 = 2$ , for the common-mode gain measurement, an input of +4 mV is also applied, and the measured output voltage is about 173 µV, so  $A_c = 0.173/4 =$ 0.043, hence CMRR is 33.351 dB, and the output resistance is 61.274 k $\Omega$ . The power dissipation of the differential amplifier circuit is 6.66 mW compared with that of 6.02 mW [5]. The results obtained from simulation are in good agreement with the calculated values.

Figure 4. Designed circuit.

#### 6. Discussions

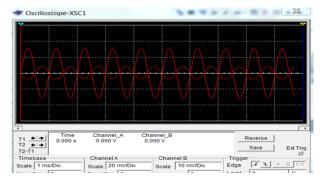

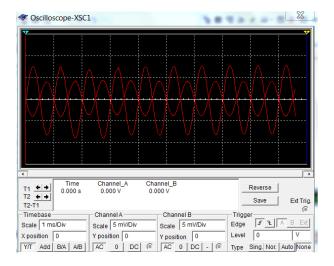

The voltages in the circuit can be varied according to the changing of voltage values at the drain of transistor  $T_5$ , which is  $V_1$ , and changing  $I_0/I_R$  value to show the effect of  $I_0$ . So two cases are considered, the first, is illustrated in the first two rows of Tables. 1, 2, and 3., for  $V_1 = 2.5$  V and 1 V at  $I_0/I_R = 812 \,\mu A/800 \,\mu A$ . The second is shown in the third row of these tables for which  $I_0/I_R = 612 \,\mu A/600 \,\mu A$  at  $V_1 = 2$  V. The (W/L) ratios for  $T_6$  and  $T_7$ , the differential pair transistors, shown in Table. 2, is decreasing with decreasing  $V_1$ , this is due to decrease in gate-to-source voltages. Both the differential gain and the common mode rejection ratio are also decreasing, with decreasing in  $V_1$ , as shown in Table. 3, and this because of decreasing in the transconductance parameter which in turn related to (W/L) ratio. The output resistance and common mode gain are unchanged in this case. The values in the third row, are compared with the calculated values obtained from design. Approximately, same values obtained for (W/L) ratio, differential gain, and the common mode rejection ratio with a decrease in common mode gain when output current decreases, but the output resistance is increased in this case due to inverse relation with output current. The amplified output voltages together with the input voltages obtained from the simulation process of the differential amplifier are shown in "Fig. 5", "Fig. 6", and "Fig. 7", respectively.

| V <sub>1</sub> | V <sub>GS1</sub> | V <sub>GS2</sub> | V <sub>GS3</sub> | V <sub>DS3</sub> | V <sub>GS5</sub> | $V_{DS5}$ | V <sub>GS6</sub> | V <sub>GS7</sub> | $V_{DS6}$ | $V_{DS7}$ | $V_{R1}$ | $V_{R2}$ |

|----------------|------------------|------------------|------------------|------------------|------------------|-----------|------------------|------------------|-----------|-----------|----------|----------|

| 2.5 V          | 4.152 V          | 4.152 V          | 4.5 V            | 3.696 V          | 3.348 V          | 4 V       | 1.5 V            | 1.5 V            | 1.419 V   | 1.419 V   | 2.081 V  | 2.081 V  |

| 1 V            | 4.89 V           | 4.889 V          | 3.002 V          | 2.222 V          | 4.108V           | 4.019 V   | 2.979 V          | 2.979 V          | 2.899 V   | 2.899 V   | 2.08 V   | 2.08 V   |

| 2 V            | 4.441 V          | 4.44 V           | 4.001 V          | 3.119 V          | 3.558 V          | 3.999 V   | 1.999 V          | 1.999 V          | 2.433 V   | 2.433 V   | 1.556 V  | 1.556 V  |

Table 1. Voltages Values of differential amplifier circuit.

Table 2. Width-to-length ratios of transistors' circuit.

| V <sub>1</sub> | $(W/L)_1$ | $(W/L)_2$ | $(W/L)_3$ | $(W/L)_4$ | $(W/L)_5$ | $(W/L)_6$ | $(W/L)_7$ |

|----------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 2.5 V          | 1.8579    | 1.8579    | 1.5203    | 1.5203    | 3.4114    | 39.4716   | 39.4716   |

| 1 V            | 1.2029    | 1.2029    | 4.7877    | 4.7877    | 1.9454    | 2.3971    | 2.3971    |

| 2 V            | 1.1624    | 1.1624    | 1.5689    | 1.5689    | 2.159     | 7.2696    | 7.2696    |

Table 3. Performance parameters.

| $V_1$ | $g_m$   | R <sub>o</sub> | A <sub>d</sub> | A <sub>C</sub> | CMRR  |  |

|-------|---------|----------------|----------------|----------------|-------|--|

| 2.5 V | 0.0023  | 61.576 kΩ      | 5.774          | 0.0413         | 42.91 |  |

| 1 V   | 0.00055 | 61.576 kΩ      | 1.423          | 0.04           | 30.84 |  |

| 2 V   | 0.00084 | 81.967 kΩ      | 2.1479         | 0.0309         | 36.84 |  |

## 7. Conclusions

For MOS differential amplifier circuit, the biasing circuit considered is modified Wilson current mirror with four transistors architecture since this circuit provides an increase in the output resistance for better performance. The analysis of width-to-length ratio, common-mode gain, differential-mode gain, and common-mode rejection ratio are performed with MATLAB computer program version 8.1.0.604(R2010a). The circuit is implemented in Multisim 9. Both, a change in applied voltage at the output and a change in output current, for the biasing circuit affect the performance parameters. A better (W/L) ratio is obtained when the voltage at the output of biasing circuit is decreased but this cause a decrease in differential gain and the common mode rejection ratio. The output resistance for current mirror is 2.297 M $\Omega$  and it can be enhanced by decreasing the output current of the biasing circuit. For differential amplifier circuit, CMRR is 33.351 dB, output resistance is 61.274 k $\Omega$ , and power dissipation is 6.66 mW.

Figure 5. Output and input voltages of differential amplifier circuit at  $V_1 = 2.5$  V.

Figure 6. Output and input voltages of differential amplifier circuit at  $V_1 = 1$  V.

Figure 7. Output and input voltages of differential amplifier circuit at  $V_1 = 2$  V, and  $I_0/I_R = 612 \ \mu\text{A}/600 \ \mu\text{A}.$

#### 8. References

- 1. Cheng, K.H., Chen, C.C., and Li, P.Y. (2005). "A High Accurate and High output Impedance Current Mirror". Tamkang University, Taiwan, R.O.C.

- 2. Tarun, N., Suman, S., and Ghost, P.K. (2014). "Design of Low Voltage Improved Performance Current Mirror". IISTE. Control Theory and Informatics, Vol.4, No.2.

- 3. Gray, P.R., Hurst, P.J., Lewis, S.H., and Meyer, R.G. (2001). "Analysis and Design of Analog Integrated Circuits". Fourth Edition. John Wiley & Sons.

- 4. Sharma, R., Gupta, N., and Kumar, A. (2014). "*Comparative analysis of different current mirror using* 0.35 μm and its application". IJARCSEE. Vol.3, Issue.6.

- 5. Shilpa, S. and Srilatha, J. (2017). "Design and Analysis of High Gain Differential Amplifier Using Various Topologies". IRJET. Vol.04, Issue.05.

- 6. Bangadkar, B., Lamba, A., and Bhure, V. (2015). "*Study of Differential Amplifier using CMOS*". IJERGS. Vol.3, Issue.2. Part.2.

- Prodanov, V.I. and Green, M.M. (1997). "A Differential Active Load and its Applications in CMOS Analog Circuit Designs". IEEE Transactions on Circuits and Systems-II: Analog and Digital Signal Processing. Vol.44, No.4.

- Tang, Y. and Geiger, R.L. (2002). "A Highly Linear CMOS Amplifier for Variable Gain Amplifier Applications". IEEE. The 2002 45<sup>th</sup> Midwest Symposium on Circuits and Systems.

- 9. Tiwari, B. and Dhanoa, J.K. (2015). "Comparison of Current Mirror Circuits Using PSpice Simulation Tool". IJECT. Vol.6, Issue 3.

- 10. Neamen, D.A. (2010). "*Microelectronics: Circuit Analysis and Design*". Fourth Edition. McGraw-Hill.

- 11. Otto, S.R. and Denier, J.P. (2005). "An Introduction to Programming and Numerical Methods in MATLAB". Springer-Verlag London Limited.

- 12. National Instruments, Electronics Workbench Group. (2009). "NI Multisim: User Manual" National Instruments Corporation.